| Electró    | Título: Rabbit 4000  Autor: Sergio R. Caprile, Senior Engineer |             |  |  |  |  |

|------------|----------------------------------------------------------------|-------------|--|--|--|--|

| Revisiones |                                                                | Comentarios |  |  |  |  |

| 0          | 31/10/06                                                       |             |  |  |  |  |

|            |                                                                |             |  |  |  |  |

Cila

Tutorial: CTU-008

El presente es un tutorial sobre microprocesadores Rabbit 4000, el tercer integrante de la familia de microprocesadores Rabbit, basados en la arquitectura de Z-80/180. El tutorial cubre las principales diferencias y mejoras de estos procesadores con respecto al Rabbit 3000, por lo que se recomienda la lectura de los tutorials sobre Rabbit 3000 (CTU-003), y Rabbit 2000 (CTU-002), dependiendo del grado de conocimientos previos sobre la familia Rabbit, así como también del comentario técnico (CTC-008) que describe las modificaciones para la revisión A del Rabbit 3000.

# Índice de contenido

| ntroducción                             | 2 |

|-----------------------------------------|---|

| Novedades                               | 2 |

| Principales diferencias con Rabbit 3000 | 2 |

| Mejoras y diferencias                   |   |

| Manejo de Memoria                       | 3 |

| CPU                                     | 4 |

| Bus auxiliar de I/O                     |   |

| Periféricos en chip                     |   |

| Ports I/O paralelo                      |   |

| Ports Serie                             | 5 |

| Timers                                  | 6 |

| Captura de eventos.                     |   |

| I/O Strobes y I/O Handshake             |   |

| Acceso directo a memoria (DMA)          | 7 |

| Ethernet 10Base-T.                      |   |

| Hardware breakpoints                    |   |

| PWM                                     |   |

|                                         |   |

CTU-008

# Introducción

Rabbit Semiconductor se forma expresamente para diseñar microprocesadores orientados a control de pequeña y mediana escala; su tercer producto es el microprocesador Rabbit 4000. Siendo un procesador de 8-bits, su performance es superior a la de muchos procesadores de 16-bits del mercado, sin perder la eficiencia de una arquitectura de 8-bits.

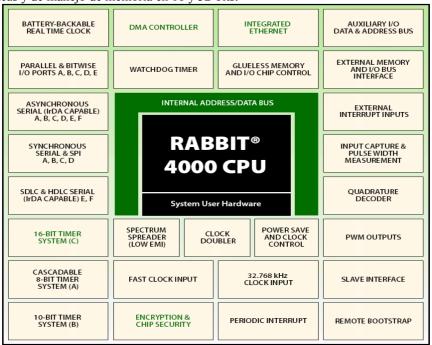

El Rabbit 4000 puede operar con un clock de hasta 60MHz, maneja hasta 16MB de memoria física, posee una interfaz Ethernet 10Base-T integrada, ocho canales de DMA, seis puertos serie, más de cuarenta entradas y salidas digitales, decodificador en cuadratura, salidas PWM, y la capacidad de capturar y medir pulsos.

El set de instrucciones ampliado incluye una gran cantidad de instrucciones para realizar operaciones aritméticas, lógicas y de manejo de memoria en 16 y 32-bits.

#### **Novedades**

- Encapsulado de 128 pines, TFBGA ó LQFP. Clock de hasta 60MHz. Rango de temperatura comercial e industrial.

- Operación a 1,8V el core; 1,8 ó 3,3V las entradas y salidas. Las entradas no son 5V-tolerant

- Menor consumo por MHz que Rabbit 3000.

- Menor cantidad de ports paralelo que R3000, pero mayor versatilidad de asignación de pines a periféricos.

- Más timers

- 8 canales de DMA

- Ethernet 10Base-T integrada y con DMA.

- Detector de cuadratura de 8- ó 10-bits (igual que R3000A)

- PWM con posibilidad de interrupción y supresión de pulsos (igual que R3000A), más DMA

- Modo usuario y modo supervisor, protección de memoria y stack (igual que R3000A)

- Instrucciones para optimizar la encripción de datos (igual que R3000A) y especialmente para AES

- Instrucciones aritméticas, lógicas y de acceso a memoria en 16- y 32-bits

## Principales diferencias con Rabbit 3000

|                                                              | R4000  | R3000  |

|--------------------------------------------------------------|--------|--------|

| Frecuencia máxima de reloj                                   | 60 MHz | 54 MHz |

| Frecuencia máxima de cristal (puede duplicarse internamente) | 60 MHz | 27 MHz |

|                                                            | R4000                  | R3000            |

|------------------------------------------------------------|------------------------|------------------|

| Tensión de operación (core)                                | 1,8V                   | 2.2.1/           |

| Tensión de operación (I/O)                                 | 3,3 V                  | 3,3 V            |

| Tensión máxima en pines de I/O                             | 3,6 V                  | 5,5 V            |

| Corriente de operación                                     | 0,35 mA/MHz a 1.8 V    | 2 mA/MHz a 3.3 V |

| Líneas de address en Aux I/O bus                           | 8                      | 6                |

| Ancho de palabra de bus de datos                           | 8/16-bits              | 8-bits           |

| Líneas de address, capacidad de memoria sin bank switching | 24, 16MB               | 20, 1MB          |

| Soporte para SRAM con acceso por páginas                   | 8/16-bits              |                  |

| Hardware breakpoints                                       | 7                      |                  |

| Cantidad de ports de I/O de 8 bits                         | 5                      | 7                |

| Canales de DMA                                             | 8                      |                  |

| Ethernet 10Base-T integrada                                | 1                      |                  |

| Timers de 16-bits                                          | 1, 4 canales set/reset |                  |

| Timers de 8-bits                                           | 10                     | 10               |

# Mejoras y diferencias

# Manejo de Memoria

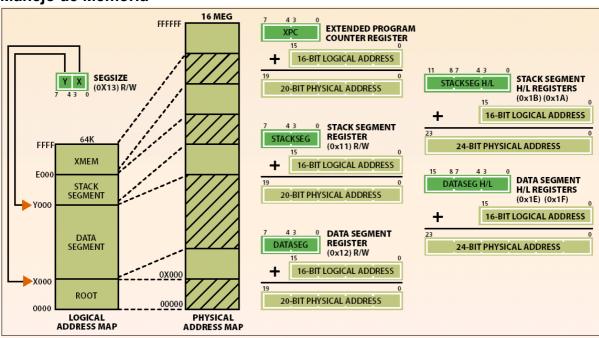

La unidad de manejo de memoria opera ahora sobre un espacio físico de 16MB. En vez de modificar los registros existentes, se han agregado nuevos registros, de modo que una escritura sobre los anteriores resulta en el correcto seteo de los nuevos, permitiendo la operación con un espacio de 1MB en compatibilidad con los procesadores anteriores.

La unidad de interfaz a memoria permite además realizar bank switching de una forma simple.

### **CPU**

La CPU Rabbit 4000 incorpora 214 nuevas instrucciones, con mayor soporte para loops largos y números de 16-bits, generando mayor densidad de código, como por ejemplo DWJNZ (Decrement Word and Jump if Not Zero) y JRE (Jump Relative Extended), versiones 16-bits de DJNZ (loop counter por excelencia) y JR, respectivamente. De igual modo, la carga del nuevo registro XPC extendido (LXPC), se realiza desde HL en sólo dos ciclos de clock, optimizando la transferencia de control entre segmentos de código en xmem.

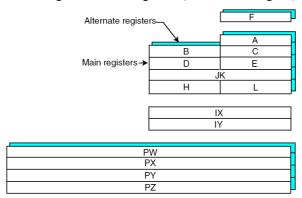

Entre los registros, encontramos cuatro nuevos registros índice de 32-bits (PW, PX, PY, PZ), y uno de 16-bits (JK), todos con sus correspondientes versiones alternativas.

El nuevo registro de 16-bits permite concatenarse con el par HL (acumulador de facto para instrucciones de 16-bits) formando pareja con BCDE, con el fin de incorporar dos registros de 32-bits de propósitos generales, sobre los cuales se pueden hacer algunas operaciones aritméticas, lógicas, y rotaciones.

Los nuevos registros de 32-bits son funcionalmente similares a IX e IY. Su principal utilidad es la de ser punteros tanto en memoria lógica como física. Esta distinción se realiza observando el estado de la palabra más significativa: las direcciones lógicas son cantidades de 16-bits, y la palabra alta se completa con todos 1's. Caso contrario, se interpreta como una dirección física. De este modo, es posible habilitar o no la utilización de la MMU en cada instrucción que haga uso de estos punteros, de forma automática. Existen instrucciones especiales para facilitar la carga de direcciones lógicas en estos registros (LDL: LoaD Logical).

Muchas instrucciones de carga de registros en modo indexado pueden utilizar estos nuevos punteros como índice, para cargas desde 8-bits hasta 32-bits. Además, existen instrucciones de "carga lejana" (LDF: LoaD Far) que permiten utilizar direccionamiento directo en memoria física, tanto en 8, 16, ó 32-bits.

En síntesis, el Rabbit 4000 es un CISC, y esto se ha explotado de forma de poder lograr una CPU de 8-bits con características interesantes de procesamiento en 16 y 32-bits, y un mapa de memoria física de 24-bits, permitiendo reducir y optimizar los tiempos de ejecución y la densidad del código, manteniendo el esquema de MMU tradicional de la familia, extendido a 24-bits, y permitiendo mayor operación sobre el mapa de memoria física. El acceso a memoria puede hacerse tanto en un bus de 8 como de 16-bits, aprovechando además el modo de acceso por página de algunas memorias SRAM.

| Select |   | Mnemonic | Function                        |

|--------|---|----------|---------------------------------|

| 0      | 0 | R3K_MODE | Rabbit 3000 instruction set     |

| 0      | 1 | Mode_01  | Enable 6D prefix page           |

| 1      | 0 | Mode_10  | Enable 6D and 7F prefix pages   |

| 1      | 1 | R4K_MODE | Enable full Rabbit 4000 mapping |

A fin de mantener una compatibilidad inmediata con Rabbit 3000, el Rabbit 4000 posee cuatro modos de operación, en los cuales habilita parte de sus nuevas instrucciones, de modo de facilitar una migración paulatina a sus nuevas prestaciones.

#### Bus auxiliar de I/O

El bus auxiliar de I/O tiene ahora ocho líneas de direcciones, se emplean los dos LSb del Port B como A7 y A8.

## Periféricos en chip

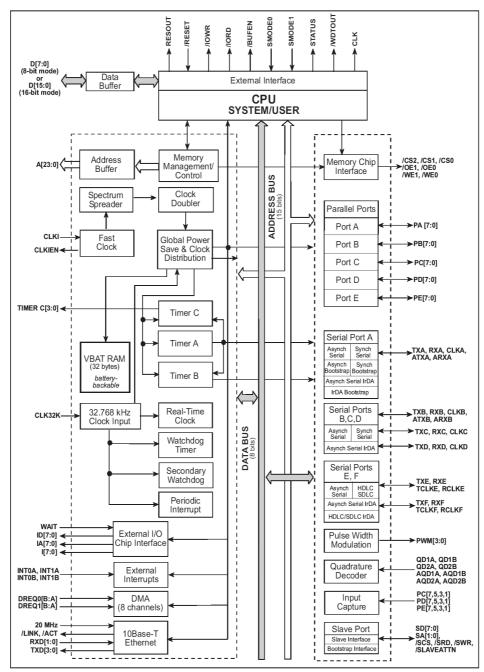

El diagrama que figura a continuación muestra un esquema de la estructura interna del Rabbit 4000, donde pueden observarse, entre otras cosas, los diferentes bloques internos que lo componen y los diversos periféricos que han sido incluidos en el mismo.

### Ports I/O paralelo

Rabbit 4000 dispone de 40 líneas de entrada/salida, repartidas en cinco ports de 8 bits designados como *port A*, *B*, *C*, *D*, y *E*. Los pines utilizados tienen funciones alternativas en alguno de los diversos periféricos internos. Los ports *D* y *E* tienen la capacidad de sincronizar sus salidas con un timer. Ambos, junto con el port *C*, pueden configurarse como open drain.

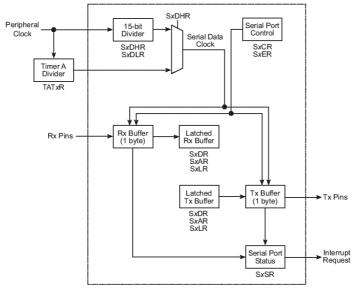

## **Ports Serie**

El Rabbit 4000 tiene seis ports serie, designados como *port A, B, C, D, E y F*. Todos pueden funcionar en modo asincrónico, pero los ports *A, B, C, y D* pueden además funcionar en modo sincrónico. Los ports *E y F* soportan además comunicaciones SDLC/HDLC. Todos los ports soportan un modo opcional RZ (Return to Zero) con timing de 3/16 (SIR) ó 1/4 (MIR) de bit; esta opción se utiliza normalmente para IrDA. El timing puede tomarse del Timer A, como en Rabbit 3000, o de unos divisores de 15-bits para tal efecto:

Los ports serie presentan una gran flexibilidad para el control por DMA, permitiendo una operación fluida en la cual la CPU sólo debe atender interrupciones en caso de errores.

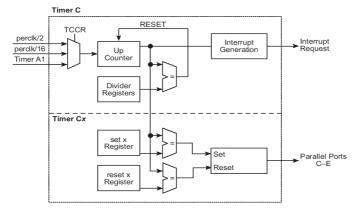

### **Timers**

El diagrama a continuación muestra la estructura del timer C, el cual es en realidad un contador ascendente de módulo variable. Incluye cuatro canales con registros de comparación que permiten setear y resetear una salida en determinadas cuentas, pudiendo utilizarse para simplificar el control de motores paso a paso, generar señales PWM multifase, etc. También incorpora una pareja de registros especiales que le permiten ser controlado por los controladores DMA.

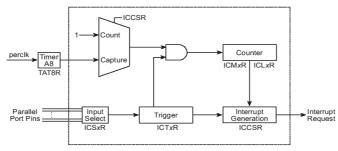

## Captura de eventos

El módulo de captura de eventos soporta además el ser utilizado para contar eventos externos, es decir, además de arrancar y parar un contador interno mediante la detección de flancos, permite ser utilizado para contar esos flancos:

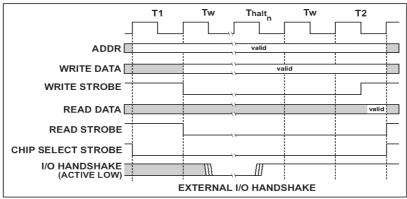

# I/O Strobes y I/O Handshake

Los I/O Strobes pueden configurarse tanto en el port E como en los ports C y D.

El esquema tradicional de I/O strobes no permitía la inserción de ciclos de espera o señalización de fin de transacción de forma dinámica desde el periférico. En R4000, puede habilitarse cualquiera de los pines del port E para funcionar como I/O Handshake, permitiendo que el periférico pueda demorar la operación de I/O por un número de ciclos adicionales, pudiendo configurarse un timeout para resolver el caso de un sistema de periféricos en mal funcionamiento

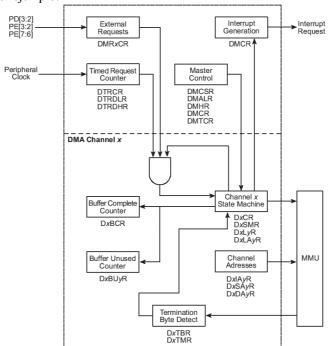

## Acceso directo a memoria (DMA)

El Rabbit 4000 incorpora ocho canales independientes de DMA, con capacidad de transferir datos entre la memoria, periféricos internos, o periféricos externos. Los mismos poseen un esquema de prioridades que permite limitar la cantidad de ciclos que los controladores roban a la CPU, y la que comparten entre ellos.

Los controladores de DMA emplean direcciones de memoria física, por lo que no utilizan ni necesitan utilizar la MMU. Todos los accesos directos a memoria utilizan los registros y señales de control de los correspondientes bancos de memoria, por lo que todos los seteos permanecen en efecto. Lo mismo ocurre para los accesos a I/O en espacio externo.

En vez de registros de control, estos controladores emplean descriptores en memoria, los cuales pueden, a su vez, formar listas encadenadas. De esta forma, ingresando en un grupo de registros la dirección del primer descriptor, es posible iniciar una secuencia de operaciones que involucre inicialización y control de periféricos y transferencias de datos, por ejemplo.

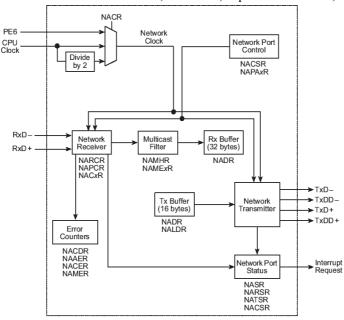

### **Ethernet 10Base-T**

El controlador integrado Ethernet fue diseñado para operar conjuntamente con los controladores DMA, utilizando dos de éstos para sí. Provee un buffer de transmisión de 16-bytes y uno de recepción de 32-bytes, insertando y chequeando automáticamente tanto preámbulo como CRC, así como también manejando todo lo relativo a la operación sobre Ethernet como colisiones, reintentos, exponential backoff, etc.

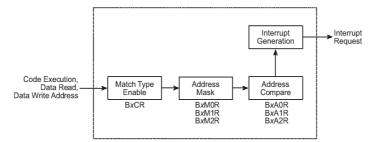

# Hardware breakpoints

Estos siete registros de 24-bits tienen como función principal el facilitar el debugging en circuito, permitiendo la generación de interrupciones de alta prioridad cuando se accede a una dirección en particular, sea ejecutando o accediendo a un dato.

# **PWM**

El generador de PWM es mayormente igual al del R3000A, con el agregado de un par de registros que permiten realizar el control del periférico mediante un controlador DMA.